Chips stall at interfaces.

Power density rises.

Boundaries saturate.

Heat accumulates.

Losses compound.

Performance flatlines.

What changes

Across internal testing and external characterisation (including IEEE EPEPS), nSD-I has demonstrated:

- ~2× improvement in effective heat extraction

versus conventional copper-based interface interposer / RDL approaches

meaningful reductions in junction-to-ambient ΔT

at comparable power densities - ~40% improvement in electrical transport

at key interfaces

reduced resistive losses

reduced localised heating - improved thermal uniformity

reduced hotspot-driven degradation - lower effective thermal stress

longer usable lifetimes - cost parity with, or lower cost than,

the underlying wafer or substrate

In practice, these gains are realised at the interposer and RDL layers, where thermal, electrical, and mechanical limits most directly constrain advanced packages.

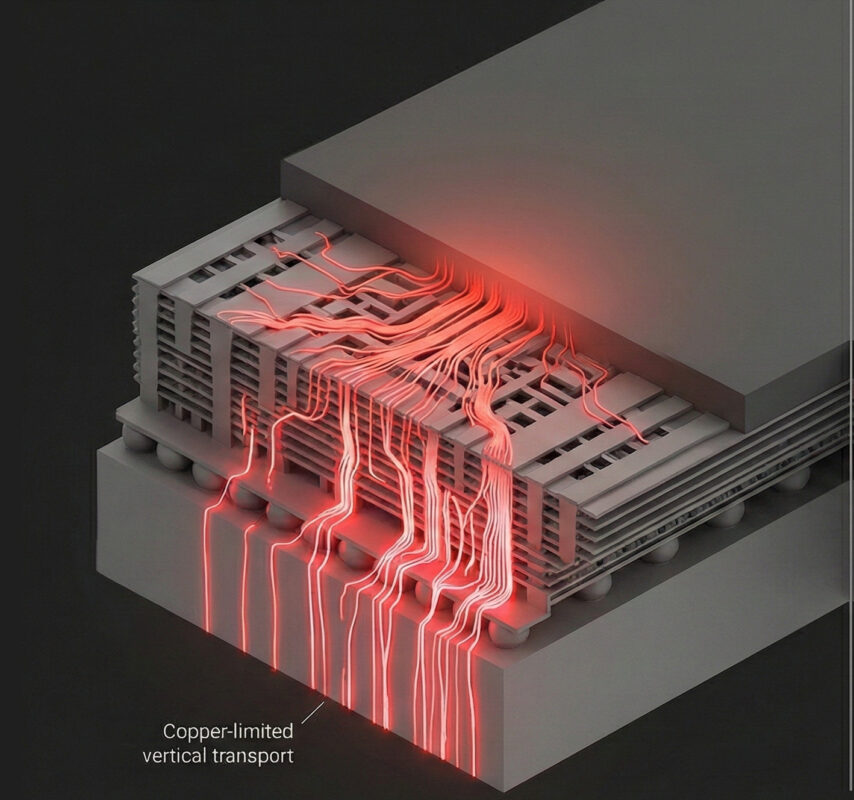

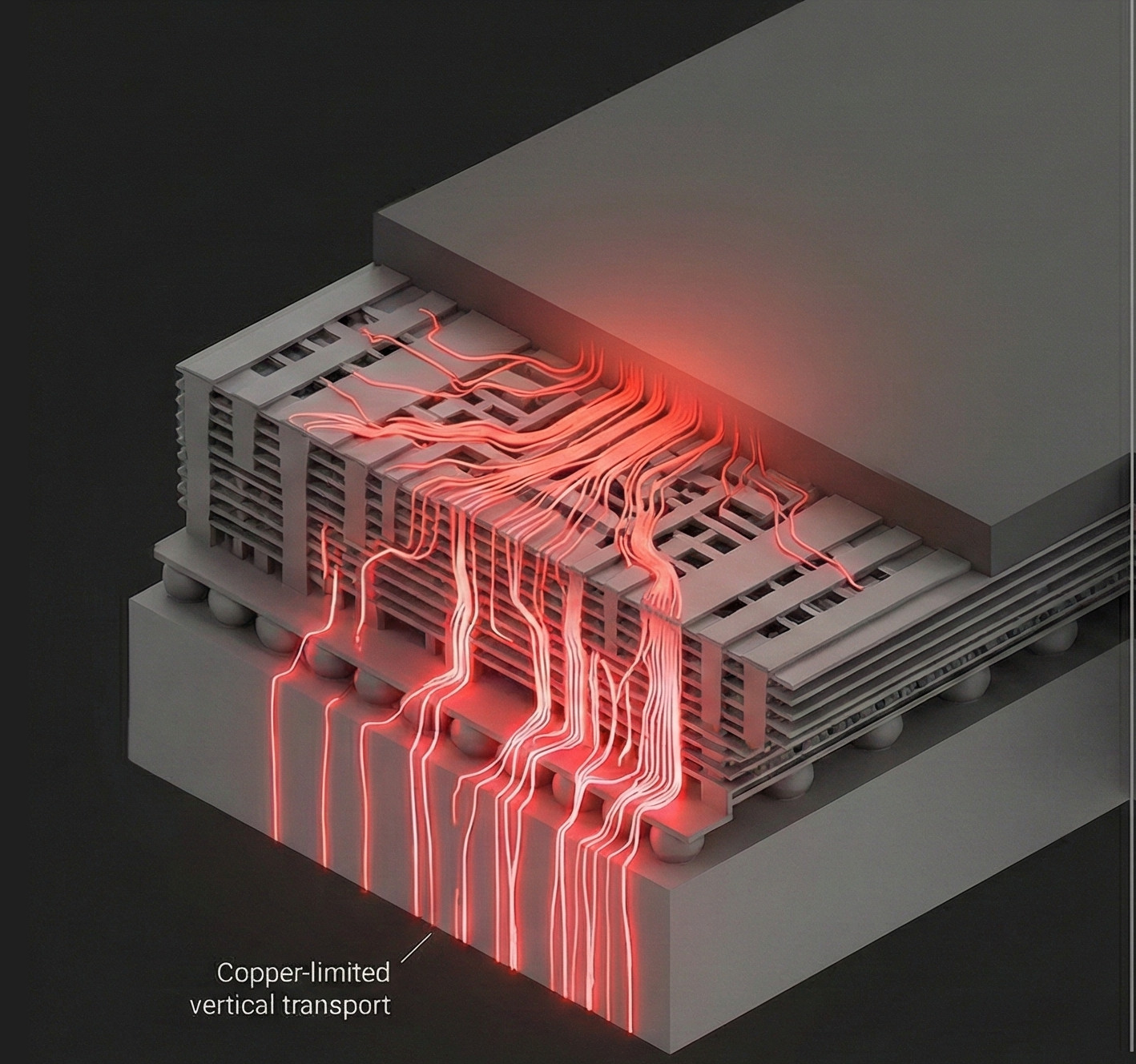

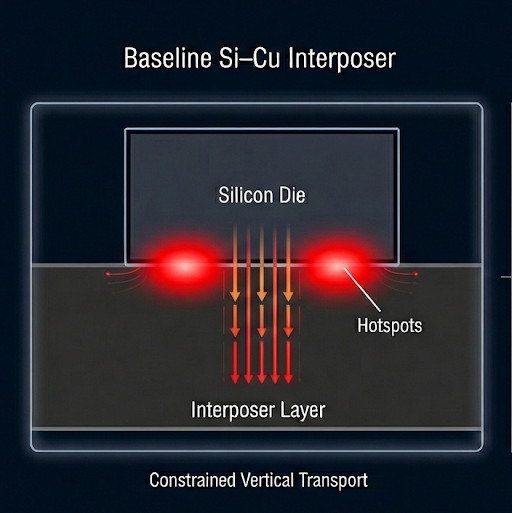

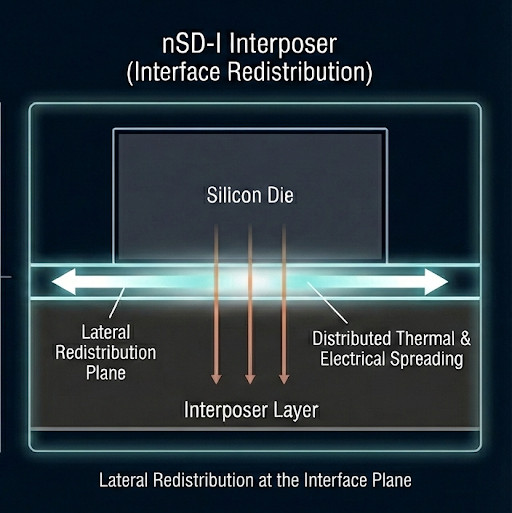

Baseline interposer (left): Vertical transport constrained at the interface, creating localized hotspots.

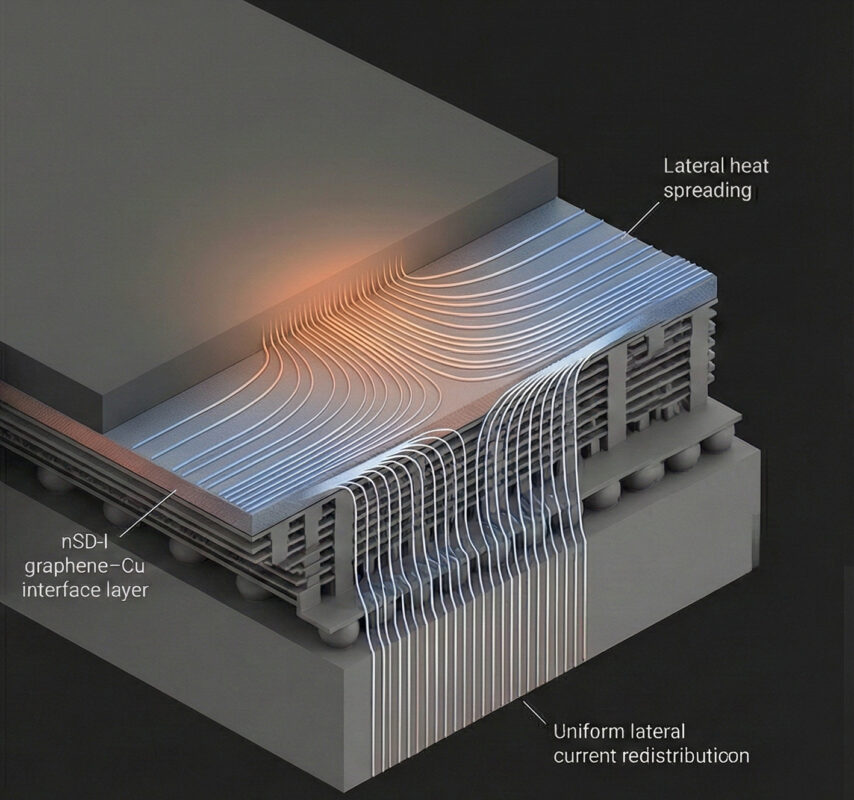

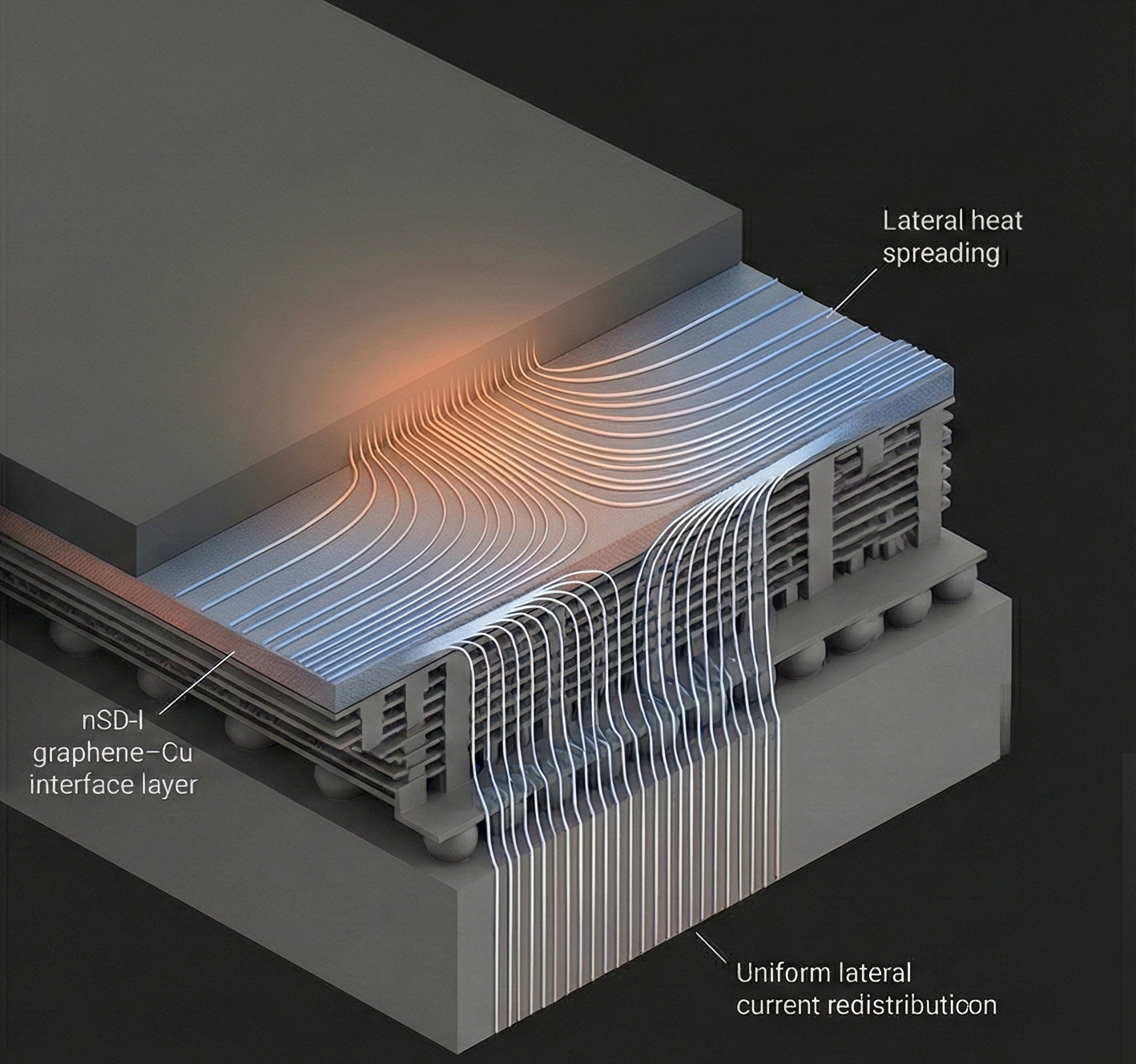

nSD-I interposer (right): Lateral redistribution at the interface plane reduces peak temperature and electrical stress without changing the vertical stack.

Illustrative schematic. Transport paths shown for conceptual clarity; not to scale.

The result

- higher sustained performance

- less thermal overdesign

- better performance per dollar

System gains depend on package architecture and integration depth.

What we do

Partners bring their designs.

Their substrates.

Their packaging stacks.

We engineer nSD-I thermal and electrical interface devices.

We embed into existing stacks.

Or co-engineer the package where needed.

We don’t manufacture chips.

We take responsibility for interface performance.

How it fits

- integrates into existing packaging flows

- avoids exotic tooling

- validated through pilots before scale

Partners keep the architecture.

We fix the interface.

Flagship deployment:

Thermal and electrical interface devices deployed as advanced packaging interposers and RDLs in high-density chip systems.